**SA56**

HTTP://WWW.APEXMICROTECH.COM (800) 546-APEX (800) 546-2739

# **FEATURES**

- DELIVERS UP TO 5A CONTINUOUS OUTPUT

- OPERATES AT SUPPLY VOLTAGES UP TO 60V

- NO "SHOOT-THROUGH" CURRENT

- THERMAL SHUTDOWN (OUTPUTS OFF) AT 160°C

- ullet SHORTED LOAD PROTECTION (to  $V_S$  or  $P_{GND}$  or SHORTED LOAD)

- NO BOOTSTRAP CAPACITORS REQUIRED

- PROGRAMMABLE ONBOARD PWM

# **APPLICATIONS**

- DC BRUSH-TYPE MOTOR DRIVES

- POSITION AND VELOCITY SERVOMECHANISMS

- FACTORY AUTOMATION ROBOTS

- NUMERICALLY CONTROLLED MACHINERY

- COMPUTER PRINTERS AND PLOTTERS

23 PIN SIP PACKAGE STYLE EX

## **DESCRIPTION**

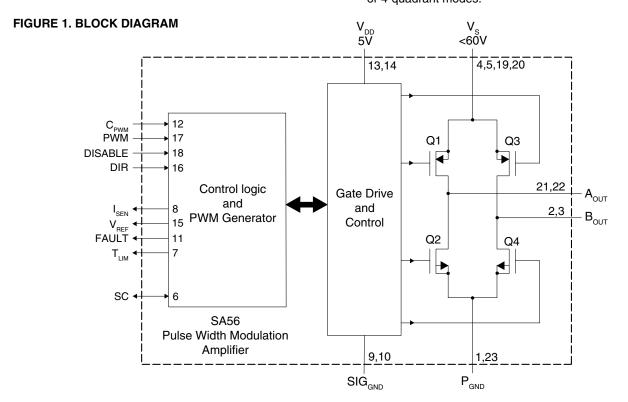

The SA56 is a 5-ampere PWM Amplifier designed for motion control applications. The device is built using a multi-technology process that combines bipolar and CMOS control circuitry with DMOS power devices in a single monolithic structure. Ideal for driving DC and stepper motors, the SA56 accommodates peak output currents up to 10 amperes. An innovative circuit that facilitates low-loss sensing of the output current has been implemented. An on-board PWM oscillator and comparator are used to convert an analog signal into PWM direction of rotation and magnitude for motor control applications. TTL or CMOS digital inputs allow direct external control in 2-quadrant or 4-quadrant modes.

ABSOLUTE MAXIMUM RATINGS **SPECIFICATIONS**

# **SA56**

## **ABSOLUTE MAXIMUM RATINGS**

SUPPLY VOLTAGE,  $V_{DD}$  SUPPLY VOLTAGE,  $V_{S}$ 5.5V 60V PEAK OUTPUT CURRENT (100mS) 10A CONTINUOUS OUTPUT CURRENT 5A POWER DISSIPATION 125W POWER DISSIPATION ( $T_A = 25^{\circ}$ C, Free Air) 10W JUNCTION TEMPERATURE, T<sub>J(MAX)</sub> ESD SUSCEPTIBILITY (Logic Pins Only) 150°C 1500V STORAGE TEMPERATURE, T<sub>STG</sub> LEAD TEMPERATURE (Soldering, 10 sec.) -40°C to +150°C 300°C JUNCTION TEMPERATURE, T -40°C to +150°C

## **SPECIFICATIONS**

| PARAMETER                                                                                                                                                                                                                                                                                                                                             | TEST CONDITIONS                                                                                                                                                                   | MIN        | TYP                                             | MAX                    | UNITS                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------|------------------------|----------------------------------------|

| V <sub>S</sub><br>VDD<br>SWITCH ON RESISTANCE, R <sub>DS</sub> (ON)                                                                                                                                                                                                                                                                                   | Output Current = 5A                                                                                                                                                               | 12<br>4.5  | 0.23                                            | 60<br>5.5<br>0.6       | V<br>V<br>Ω                            |

| N-Channel<br>SWITCH ON RESISTANCE, R <sub>DS</sub> (ON)                                                                                                                                                                                                                                                                                               | Output Current = 5A                                                                                                                                                               |            | 0.27                                            | 0.6                    | Ω                                      |

| P-Channel<br>CLAMP DIODE FORWARD DROP, V <sub>CLAMP</sub><br>LOGIC LOW INPUT VOLTAGE, V <sub>IL</sub>                                                                                                                                                                                                                                                 | Clamp Current = 5A                                                                                                                                                                | -0.5       | 1.43                                            | 0.8                    | V<br>V                                 |

| LOGIC LOW INPUT CURRENT, $\mathbf{I}_{\rm IL}$ LOGIC HIGH INPUT VOLTAGE, $\mathbf{V}_{\rm IH}$                                                                                                                                                                                                                                                        | $V_{IN} = -0.1V$                                                                                                                                                                  | -10<br>2   |                                                 | +10<br>V <sub>DD</sub> | μA<br>V                                |

| LOGIC HIGH INPUT CURRENT, I <sub>IH</sub><br>CURRENT SENSE OUTPUT                                                                                                                                                                                                                                                                                     | $V_{IN} = 5.5V$ $I_{OUT} = 1A$                                                                                                                                                    | -10<br>180 | 240                                             | 10<br>300              | μΑ<br>μΑ                               |

| CURRENT SENSE LINEARITY ERROR                                                                                                                                                                                                                                                                                                                         | $I_{\text{OUT}}^{\text{OT}} = 5A$<br>$1A \le I_{\text{OUT}} \le 5A$<br>$100 \text{ mA} \le I_{\text{OUT}} \le 5A$<br>$5A \le I_{\text{OUT}} \le 10A \text{ (Peak Currents only)}$ | .79        | 1.0<br>±1                                       | 1.32<br>±5<br>±8<br>±8 | mA<br>%<br>%<br>%                      |

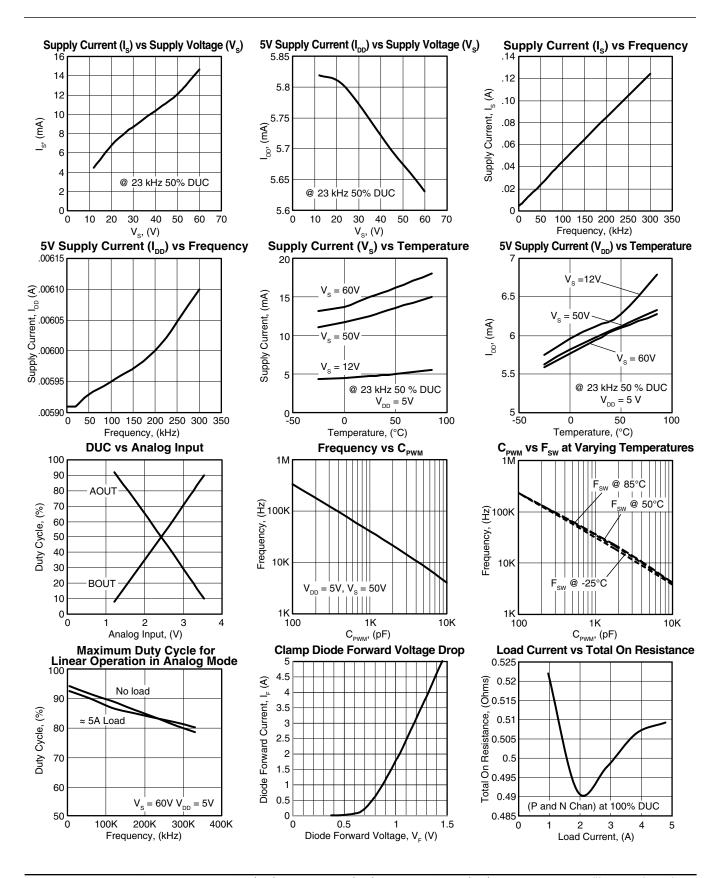

| SHUTDOWN TEMPERATURE, $T_{\rm JSD}$ QUIESCENT SUPPLY CURRENT, $I_{\rm S}$ QUIESCENT SUPPLY CURRENT, $I_{\rm DD}$ OUTPUT TURN-ON DELAY TIME, $t_{\rm Don}$ OUTPUT TURN-ON SWITCHING TIME, $t_{\rm on}$ OUTPUT TURN-OFF DELAY TIMES, $t_{\rm Doff}$ OUTPUT TURN-OFF SWITCHING TIME, $t_{\rm off}$ MINIMUM INPUT PULSE WIDTH, $t_{\rm p}$ (DIGITAL MODE) | Outputs Turn OFF No Load, $F_{SW} = 100 \text{kHz} 50\% \text{ DUC}$ No Load, $F_{SW} = 100 \text{kHz} 50\% \text{ DUC}$ No Load No Load No Load No Load No Load No Load          |            | 160<br>26<br>6<br>200<br>41<br>272<br>46<br>140 | 50<br>15               | °C<br>mA<br>mA<br>ns<br>ns<br>ns<br>ns |

| REFERENCE VOLTAGE                                                                                                                                                                                                                                                                                                                                     | I <sub>REF</sub> = 1mA                                                                                                                                                            | 2.3        | 2.5                                             | 2.7                    | V                                      |

| Vref OUTPUT CURRENT (Vref 2.5V), $I_{\rm REF}$                                                                                                                                                                                                                                                                                                        | Source Only, No current sink capability                                                                                                                                           |            |                                                 | 1                      | mA                                     |

| ANALOG INPUT RANGE FOR FULL MODULATION                                                                                                                                                                                                                                                                                                                | Load Current = 400µA                                                                                                                                                              | 1          |                                                 | 4                      | V                                      |

| HIGH CURRENT SHUTDOWN RESPONSE                                                                                                                                                                                                                                                                                                                        | Output shorted (No bypass capacitor at SCin pin)                                                                                                                                  |            | 250                                             | 800                    | ns                                     |

| THERMAL RESISTANCE, Junction to Case RESISTANCE, Junction to Air TEMPERATURE RANGE, Case                                                                                                                                                                                                                                                              | Full Temperature Range<br>Full Temperature Range                                                                                                                                  | -40        | 1<br>12.21                                      | 125                    | °C/W<br>°C/W<br>°C                     |

NOTE: These specifications apply for  $V_S = 50V$  and  $V_{DD} = 5V$  at  $25^{\circ}C$ , unless otherwise specified.

OPERATING CONSIDERATIONS SA56

8

9.10

11

12

15

16

$13,14 \, V_{DD}$

$V_{RFF}$

DIR

$I_{SEN}$

SIGGND

**FAULT**

$C_{PWM}$

be logic low. When a junction temperature

exceeds approximately 160°C this pin will

change to logic high and the output will be

latched off. Grounding this pin disables over

temperature protection. This pin should be

left open if over temperature protection is

Current Sense output and programmable

current limit. A current proportional to the output current is sourced by this pin. Typi-

cally this pin is connected to a resistor for programmable current limit or transconduc-

Ground connection for all internal digital and

This pin latches high whenever the four

MOSFETs have been placed in the tristate

condition which occurs when either the high-current or the thermal protection has

An external timing capacitor is connected to

this pin to set the frequency of the internal

oscillator and ramp generator for analog

control mode. The capacitor value (pF) =  $4.05x10^{7}/F_{SW}$ , where  $F_{SW}$  = the desired

switching frequency. This pin is grounded

5V supply for input logic and low voltage

Reference voltage. Can be used at low cur-

Direction of rotation control; In 2 quadrant, digital control, determines the active output

rent for biasing analog loop circuits.

desired but the flag is not used.

low-current analog circuitry.

for digital control mode.

analog circuitry.

tance operation.

engaged.

#### **GENERAL**

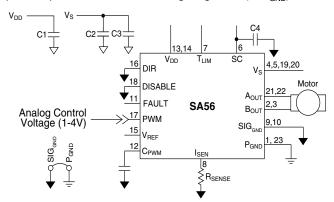

Please read "SA56 Design Ideas" that covers the various SA56 applications in considerable detail. Also see Application Note 1 "General Operating Considerations" which covers stability, power supplies, heat sinking, mounting, and specification interpretation. Visit www.apexmicrotech.com for design tools that help automate tasks such as calculations for stability, internal power dissipation, current limit, heat sink selection, Apex's complete Application Notes library, Technical Seminar Workbook and Evaluation Kits.

#### **GROUND PINS**

The two  $SIG_{GND}$  pins, 9 & 10, are for input signal grounds. Pins 1 and 23,  $P_{GND}$ , are power grounds. The  $P_{GND}$  &  $SIG_{GND}$  pins are connected at one point inside the IC. It is also recommended the user connect both pins at a single point on the board in a way that no current flows through that connection.

## **POWER SUPPLY BYPASSING**

Bypass capacitors to power supply terminals  $V_{S}$  and  $V_{DD}$  must be connected physically close to the pins to prevent erratic, low-efficiency operation and excessive ringing at the outputs. Electrolytic capacitors, at least 10  $\mu F$  per output ampere are required for suppressing  $V_{S}$  to  $P_{GND}$  noise. High quality ceramic capacitors (X7R) 1  $\mu F$  or greater should also be used. Only capacitors rated for switching applications should be considered. The bypass capacitors must be located as close to the power supply pins as possible. Due to the very fast switching times of the outputs, the inductance of 1 inch of circuit trace could cause noticeable degradation in performance. The bypassing requirements of  $V_{DD}$  are less stringent, but still necessary. A 0.1  $\mu F$  to 0.47  $\mu F$  capacitor connected directly between the  $V_{DD}$  and  $SIG_{GND}$  pins will suffice.

| PIN DESCRIPTIONS |                  |                                                                                                                                                                                                                                                                                                                                                                                                                       |       |                  | FETs. This pin should be grounded in analog                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #            | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                           |       |                  | control mode.                                                                                                                                                                                                                                                                                                                                                                                               |

| 1,23             | $P_{GND}$        | Power high current ground return path of the motor.                                                                                                                                                                                                                                                                                                                                                                   | 17    | PWM              | CMOS/TTL input for digital PWM control, or 1-4V analog input for duty cycle control in                                                                                                                                                                                                                                                                                                                      |

| 2,3              | B <sub>OUT</sub> | Half bridge output B                                                                                                                                                                                                                                                                                                                                                                                                  |       |                  | analog control mode.                                                                                                                                                                                                                                                                                                                                                                                        |

| 4,5,<br>19,20    | V <sub>s</sub>   | High voltage supply                                                                                                                                                                                                                                                                                                                                                                                                   | 18    | DISABLE          | Following a fault, pulling the DISABLE pin HIGH and then LOW will reset a latched                                                                                                                                                                                                                                                                                                                           |

| 6                | SC               | The short-circuit protection circuits will sense a direct short from either output ( $A_{OUT}$ or $B_{OUT}$ ) to $P_{GND}$ or $V_S$ – as well as across the load. If the high-current protection circuit engages it will place all four MOSFETs in the tristate state (high-impedance output). The SC output, pin 6, will go HIGH though not latch, thereby denoting that this protection feature has been triggered. |       |                  | fault condition. (When pulled HIGH, all four output MOSFETs are disabled. A logic LOW on this pin allows the four output FETs to function normally.) When the DISABLE and FAULT pins are tied to a microcontroller, the FAULT pin will generate an interrupt in the microcontroller, so that the interrupt, can in turn, generate a pulse on the DISABLE pin. When a fault occurs, the SA56 fault circuitry |

| 7                | T <sub>LIM</sub> | Temperature limit, CMOS. This pin can be used as a flag for an over-temperature condition. Under normal operation this pin will                                                                                                                                                                                                                                                                                       | 21,22 | A <sub>OUT</sub> | will be reset.<br>Half bridge output A                                                                                                                                                                                                                                                                                                                                                                      |

SA56 OPERATING CONSIDERATIONS

#### MODES OF OPERATION

The following chart shows the 3 modes of operation.

| Mode                      | C <sub>PWM</sub><br>pin 12                 | PWM<br>pin 17                         | DIR<br>pin 16             | A <sub>out</sub><br>pins 21, 23                                                                                       | B <sub>OUT</sub><br>pins 2, 3                                                                                         |

|---------------------------|--------------------------------------------|---------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 2 Quadrant – Analog Mode  | Connect ca-<br>pacitor to set<br>frequency | Analog control<br>voltage<br>(1 – 4V) | Low (SIG <sub>GND</sub> ) | Control voltage<br>greater than V <sub>REF</sub> :<br>(A <sub>OUT</sub> - B <sub>OUT</sub> )< 0<br>average<br>voltage | Control voltage<br>greater than V <sub>REF</sub> :<br>(B <sub>OUT</sub> - A <sub>OUT</sub> )> 0<br>average<br>voltage |

| 2 Quadrant – Digital Mode | SIG <sub>GND</sub>                         | Modulation In                         | High (V <sub>DD</sub> )   | High (V <sub>s</sub> )                                                                                                | PWM                                                                                                                   |

|                           | SIG <sub>GND</sub>                         | Modulation In                         | Low (SIG <sub>GND</sub> ) | PWM                                                                                                                   | High (V <sub>s</sub> )                                                                                                |

| 4 Quadrant – Digital Mode | SIG <sub>GND</sub>                         | High (V <sub>DD</sub> )               | Modulated In              | DIR                                                                                                                   | DIR                                                                                                                   |

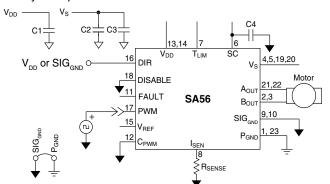

#### 4-QUADRANT - ANALOG MODE

The SA56 can operate in 4-quadrant mode with analog or digital inputs. In the analog mode, the capacitor from  $C_{\text{PWM}}$  to  $\text{SIG}_{\text{GND}}$  sets the frequency of an internal triangular ramp signal. See Figure 2. An analog voltage applied to the PWM pin is compared to a 2.5 volt reference within the SA56 thereby governing the duty cycle of the output. Note that the analog pin DIR pin 16 is connected to signal ground  $(\text{SIG}_{\text{GND}})$ .

FIGURE 2. 4-QUADRANT ANALOG OPERATION

## **OPERATING WITH DIGITAL INPUTS**

Two and 4-quadrant operation are possible with the SA56 when driven with a digital PWM signal from a microcontroller or DSP. When using a digital modulation signal, tie the  $C_{\text{PWM}}$  pin to  $\text{SIG}_{\text{GND}}$  to disable the internal oscillator and ramp generator. When operating in the digital mode, pulse widths should be no less than 100 ns and the switching frequency should remain less than 500 kHz. This will allow enough time for the output MOSFETs to reach their full on and off states before receiving a command to reverse state.

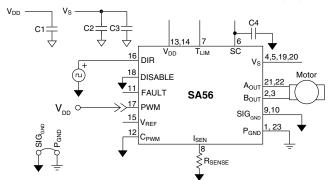

#### 2-QUADRANT - DIGITAL MODE

Two-quadrant operation of the FETs is realized by driving PWM pin 17 of the SA56 with a digital PWM signal supplied by a microcontroller or DSP, as depicted in Figure 3. When using a digital modulation signal, connect the  $C_{\text{PWM}}$  pin to  $\text{SIG}_{\text{GND}}$  to disable the internal oscillator and its companion ramp generator.

A digital PWM signal applied to the PWM pin controls the output duty cycle at one output pin while the other output pin is held "HIGH". The input at the DIR pin ( $V_{DD}$  or  $SIG_{GND}$ ) governs the output behavior. If DIR is a logic HIGH, the  $A_{OUT}$  output will be held high and the  $B_{OUT}$  output will be switched as the complement of the PWM input signal. The average output at  $A_{OUT}$  will always be greater than at  $B_{OUT}$ . Whereas if DIR is a logic LOW, the  $B_{OUT}$  output will be held "HIGH" and the  $A_{OUT}$  output will be switched.

Operating in two-quadrant mode reduces switching noise and power dissipation, but limits the ability to control the motor at very low speed.

FIGURE 3. 2-QUADRANT - DIGITAL MODE

OPERATING CONSIDERATIONS SA56

#### **4 QUADRANT DIGITAL MODE**

During four-quadrant operation a single digital PWM input includes magnitude and direction information. The digital PWM input signal is applied to the DIR pin, as shown in Figure 4, and the PWM pin is tied HIGH to  $V_{\rm DD}$ . Both pairs of output MOSFETs will switch in a locked, complementary fashion.

With a 50% duty cycle the average voltage of outputs  $A_{OUT}$  and  $B_{OUT}$  will be the same, which is half of  $V_{\rm S}$  so that the average differential voltage over each period applied to the load will therefore be zero.

Four-quadrant operation allows for smooth transitions through zero current for low-speed applications. However, power dissipation is slightly higher than in two-quadrant operation since all four output MOSFETs must switch every cycle.

FIGURE 4. 4-QUADRANT - DIGITAL MODE

## **BRAKING - DIGITAL MODE**

Under digital control, the SA56 can rapidly decelerate the motor by shunting the winding currents through the output MOSFETs. Logic LOW on the PWM input both A and B outputs high. The motor winding current circulates through the on resistance of the MOSFETs quickly slowing the motor.

The winding current can be monitored with the  $I_{SEN}$  pin during the braking of the motor. However, the current during braking circulates in the normal forward direction through one output MOSFET and is in the reverse in the other MOSFET. The current sense feature can measure only forward currents. The logic input on the DIR pin dictates which output MOSFET is used for sensing the forward current during braking.

## **PROTECTION CIRCUITS**

The most severe condition for any power device is a direct, hard-wired ("screwdriver") short from an output to ground. While the short-circuit protection will latch the output MOSFETs within 500 ns (typical), the die and package may be required to dissipate up to 500 Watts of power until the protection circuits are activated.

This energy can be destructive, particularly at higher operating voltages, so sound thermal design is critical if fault tolerance is to be established in the design. The  $V_{\rm S}$  and  $P_{\rm GND}$  pins may become very hot during this period of high current.

Thermal and short-circuit protection are included in the SA56 to prevent damage in the event that faults occur as described below:

**Short-circuit protection** – The short-circuit protection circuits will sense a direct short from either output ( $A_{OUT}$  or  $B_{OUT}$ ) to  $P_{GND}$  or  $V_S$  – as well as across the load. If the high-current protection circuit engages, it will place all four MOSFETs in the tristate state (high-impedance output). The SC output, pin 6, will go HIGH though not latch, thereby denoting that this protection feature has been triggered.

Over-current protection – When the current on the high side goes above 10 amperes peak, the over-current circuit tristates so that the four MOSFETs go into a latched fault condition.

**Thermal protection** – The thermal protection circuits will engage if the temperature of any of the four MOSFETs reaches approximately 160°C. If this occurs, the FAULT output pin will go HIGH. If the thermal protection circuit engages, it will place all four MOSFETs in the tristate state (high-impedance output). The  $T_{\text{LIM}}$  output which is normally LOW will go HIGH, though not latch, thereby denoting which of the protection features has been triggered.

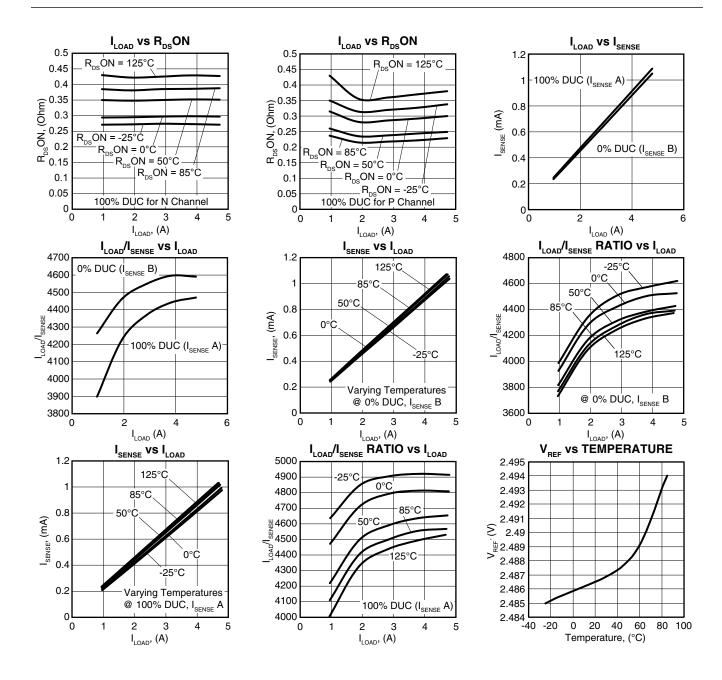

#### PROGRAMMABLE CURRENT LIMIT

The  $I_{\text{SEN}}$  pin sources a current proportional to the forward output current of the active P channel output MOSFET. The proportionality is approximately 200 microamperes per ampere of output current. Note that the  $I_{\text{SEN}}$  output is blocked during the switching transitions when current spikes are likely to be significant.

To create a programmable current limit, connect a resistor from  $\rm I_{SEN}$  to  $\rm SIG_{GND}.$  If the voltage across this resistor exceeds an internally-generated 2.75V threshold, all four output MOSFETs will be turned off for the remainder of the switching cycle. A 2.7k-Ohm resistor will set the current limit at approximately 5 amperes.

The  $I_{\rm SEN}$  output can also be used for maintaining a current control loop in torque motor applications.

#### **CURRENT SENSE LINEARITY CALCULATION**

The current sense linearity is specified in the table on page 2 and is calculated using the method described below:

- a) Define a straight line (y = mx + b) joining the two end data points where, m is the slope and b is the offset or zero crossover. Calculate the slope m and offset c using the extreme data points. Assume  $I_{\text{SENSE}}$  in the y axis and  $I_{\text{LOAD}}$  in the x axis.

- b) Calculate linear  $I_{\rm SEN}$  (or ideal  $I_{\rm SENSE}$  value,  $IS_{\rm IDEAL}$ ) using the straight line equation derived in step (a) for the  $I_{\rm LOAD}$  data points.

- c) Determine deviation from linear  $I_{SEN}$  (step (b) and actual measured  $I_{SENSE}$  value ( $IS_{ACTUAL}$ ) as shown below:

Linearity Error (%) =

$$\frac{IS_{IDEAL} - IS_{ACTUAL}}{IS_{IDEAL}} \times 100$$